金刚石衬底表面工艺(单晶/多晶/薄膜)的平整度与粗糙度对晶圆键合工艺的影响分析

金刚石凭借超高热导率(可达2000W/(m·K)以上)、优异化学惰性及宽禁带特性,成为GaN、SiC等宽禁带半导体器件异质集成的理想散热衬底,晶圆键合是实现金刚石与半导体器件集成的核心技术路径。单晶、多晶金刚石及金刚石薄膜的表面平整度(以总厚度偏差TTV、翘曲度Warp为核心指标)与粗糙度(以算术平均粗糙度Ra为核心指标),直接决定键合良率、界面强度、热阻及电学性能稳定性。本文结合表面工艺特性,系统解析其对后道晶圆键合工艺的差异化影响。

一、金刚石衬底表面核心评价指标及工艺控制范围

晶圆键合对金刚石衬底表面质量的要求极为严苛,核心指标包括粗糙度(Ra)、平整度(TTV、Warp),不同类型金刚石因晶体结构差异,表面工艺的控制难度与目标范围存在显著区别,具体参数如下:

二、不同类型金刚石衬底表面质量对晶圆键合工艺的影响

(一)单晶金刚石衬底:低粗糙度高平整度适配高端键合需求

单晶金刚石晶体结构完整、无晶粒间界,经CMP工艺可实现原子级平整表面,其表面质量对键合工艺的影响集中于精准控制与成本平衡。

在表面活化键合中,单晶金刚石Ra≤0.5nm、TTV≤10μm的表面质量,可确保氩原子束轰击后表面活化均匀,去除原生氧化物后形成致密键合界面,键合压力控制在10MPa左右即可实现室温高强度键合,界面热阻可低于10m²·K/GW。若粗糙度超出1nm,活化过程中原子束轰击易产生局部过度蚀刻,导致表面粗糙度反向增加,形成残余间隙与界面缺陷,降低键合良率与力学稳定性。此外,单晶金刚石平整度偏差过大会导致键合时压力分布不均,局部区域因接触不充分形成空隙,成为热传导与电信号传输的瓶颈。

优势在于表面质量一致性好,适配2英寸及以下小尺寸晶圆的高精度键合,是5G/6G高频器件、量子传感器等高端场景的优选;劣势为大尺寸单晶金刚石生长难度大、成本高昂,限制了晶圆级规模化键合应用。

(二)多晶金刚石衬底:平整度制约大尺寸键合良率

多晶金刚石成本低于单晶、可实现大尺寸制备,但其表面质量对键合工艺的影响更复杂,核心矛盾集中于晶粒间界导致的表面不均与应力问题。

未优化抛光的多晶金刚石表面凸起尖峰高度可达15nm,直接导致键合界面空隙率激增,键合率不足50%。通过DPP技术将尖峰高度降至1.2nm、Ra控制在0.29nm后,可实现厚膜GaN(~370μm)与多晶金刚石(~660μm)的室温表面活化键合,键合率提升至92.4%,且能耐受-55℃~250℃极端温度循环。但大尺寸(3英寸及以上)多晶金刚石的粗糙度与平整度难以全域统一,边缘区域易出现翘曲与粗糙度超标,导致键合时界面应力集中,甚至引发薄膜开裂。此外,晶粒间界的缺陷会在键合后退火过程中加剧界面态密度,需通过非晶硅纳米缓冲层调节热膨胀系数差异,缓解应力影响。

多晶金刚石的表面工艺优化方向为提升大尺寸晶圆的全域均匀性,目前已在车载功率器件、工业电源等中端散热场景实现小批量应用。

(三)金刚石薄膜:粗糙度与厚度均匀性协同影响键合可靠性

金刚石薄膜多通过CVD技术沉积于Si、SiC基底,其表面质量与薄膜-基底结合强度共同决定键合工艺适配性,粗糙度是影响界面接触与热阻的核心因素。

采用MPCVD技术制备的金刚石薄膜,若沉积过程中控制CH₄浓度低于5%、引入氩气细化晶粒,可获得Ra≤0.5nm的光滑表面,搭配等离子体辅助抛光后,可满足表面活化键合与亲水键合的严苛要求。此类薄膜与GaN键合后,界面层厚度可控制在1.5nm以内,热阻极低且电学性能稳定;若薄膜Ra>1nm,键合界面易形成微小空隙,不仅增加热阻,还会导致界面态密度升高至10¹³cm⁻²eV⁻¹,显著影响器件电信号传输效率。此外,金刚石薄膜的厚度均匀性直接关联键合压力分布,厚度偏差超过0.2μm时,局部区域易因压力不足导致键合失效,而高碳浓度沉积的薄膜表面粗糙化严重,需额外增加抛光步骤,易造成薄膜损伤与基底剥离。

金刚石薄膜适配柔性器件、超薄散热结构的键合需求,在微波器件、光电子器件领域具有潜在应用价值,其表面工艺核心在于平衡沉积效率、结晶质量与表面光滑度。

三、键合工艺适配策略与表面质量优化方向

(一)基于键合技术的表面质量适配方案

不同键合技术对金刚石表面质量的耐受度不同,需针对性匹配表面工艺指标:

1. 表面活化键合:作为金刚石基异质集成的主流技术,需严格控制Ra≤0.5nm(真空密封场景)或Ra≤1nm(常规场景),TTV≤3μm、Warp≤25μm,同时通过氩原子束活化时精准控制能量(1-2kV),避免过度蚀刻导致表面粗糙度上升。键合后可通过300-400℃退火消除界面非晶层,1000℃退火可将界面态密度降低至原有的1/5。

2. 亲水键合:对粗糙度要求与表面活化键合相当(Ra<1nm),但需控制表面OH端均匀性,避免粗糙表面导致水分子残留,形成界面空隙与应力集中,目前该技术因水分子逸出难题,在金刚石键合中应用较少。

3. 原子扩散键合:对平整度敏感度略低,但需确保Ra<2nm,通过中间层(如非晶硅、氧化铝)填补微小表面缺陷,提升键合强度与热传导效率。

(二)表面工艺优化方向

1. 单晶金刚石:开发高效低损伤CMP技术,引入新型抛光液提升速率,同时优化激光修整参数,减少后续抛光压力;2. 多晶金刚石:突破大尺寸晶圆全域抛光技术,结合晶粒取向调控减少界面缺陷,通过应力缓冲层设计平衡键合界面应力;3. 金刚石薄膜:优化CVD沉积参数(如CH₄/H₂比例、氩气掺杂量),实现沉积与初步平整一体化,降低后续抛光依赖,同时提升薄膜与基底的结合强度,避免键合过程中剥离。

四、结论

金刚石衬底的平整度与粗糙度是决定晶圆键合工艺成败的核心因素,其影响贯穿键合活化、压力施加、界面形成及退火稳定全流程:单晶金刚石凭借优异的表面均匀性适配高端高精度键合,多晶金刚石的关键突破点为大尺寸全域平整度控制,金刚石薄膜则需协同优化厚度均匀性与表面粗糙度。未来需通过表面工艺创新(如高效抛光、精准沉积调控)降低金刚石表面质量控制成本,同时结合键合技术优化(如缓冲层设计、退火工艺改进),缓解表面缺陷对键合性能的影响,推动金刚石在半导体异质集成散热领域的规模化应用。

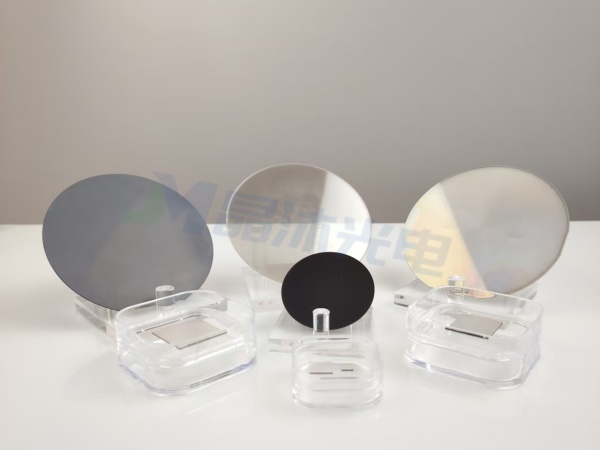

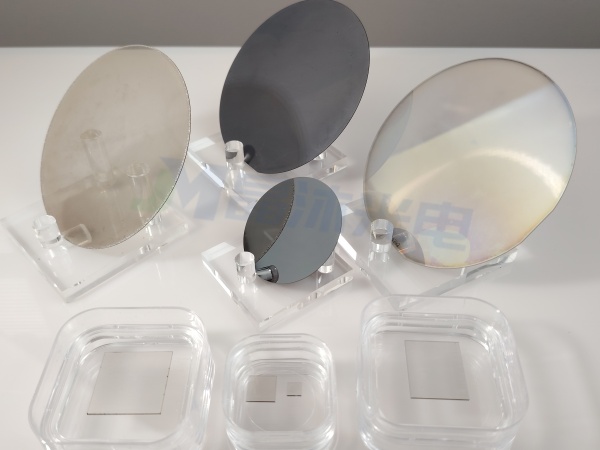

晶沐光电在金刚石衬底及薄膜领域拥有丰富的产品供应能力,可满足不同客户的多样化需求。其中:

金刚石单晶(Monocrystal)供应规格涵盖 5×5mm、10×10mm、20×20mm、30×30mm;

金刚石多晶(Polycrystal)供应规格包括 10*10mm、2inch、4inch、6inch;

金刚石薄膜(Diamond Film)涵盖碳化硅基金刚石薄膜与硅基金刚石薄膜,供应规格为 2inch、4inch、6inch,

为电子、光学、机械加工等多个领域提供高质量的金刚石材料支持,助力相关产业技术升级与创新发展。